# No need to duplicate yourself

# BuyerZone saves you time and money on COPIERS AND MORE.

Get free advice, pricing articles, ratings and quotes on Business Purchases from digital copiers, to phone systems, to payroll services and more. Visit BuyerZoneBusiness.com today to make fast and efficient business purchase decisions. At BuyerZone, you're in control. We're just here to make your work easier.

Join the millions who've already saved time and money on many of their Office Equipment purchases by taking advantage of BuyerZone's FREE, no obligation services like:

- Quotes from multiple suppliers

- Pricing articles

- Buyer's guides

- Supplier ratings

- Supplier comparisons

#### **REQUEST FREE QUOTES NOW!** Call (866) 623-5564 or visit BuyerZoneBusiness.com

# WHERE DESIGN ENGINEERS GO FIRST! DIGIKEY.COM

<u> Jiqi-Ke</u>

INE ORDERING

ORDER STATUS Roduct inde)

CONTACT US

SITE MAP About Digi-Key

#1 Breadth of Product Line#1 Availability of Product#1 Overall Performance

Source: **EE**Times Distribution Study, August 2008

IVQ-IXEN

The industry's broadest product selection available for immediate delivery

CORPORATION

1

### www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2009 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

1-800-344-4530

? Nee

000

30

PRODUCTS

000

ADDED 90 DAYS!

WHAT'S NEW

# EDN 11.26.09 contents

From magnetic to solid state, spin-free: What a long, strange storage trip it's turning out to be

24 To seriously compete with hard-drive makers, semiconductor vendors must amass a robust, sustained supply of silicon for solid-state drives. They also must address plenty of misconceptions about the newer technology's capabilities and limitations.

by Brian Dipert, Senior Technical Editor

# Lessons from the last mile

1 Schip designers' struggles to provide triple-play HD service to telephone, cable, and wireless customers are changing the nature of SOC architecture. by Ron Wilson, Executive Editor

- WinSystems highlights Atom board, CompactFlash

- 10 High-performance MSOs feature 20-GHz analog bandwidth

- 11 Stable quartz oscillator uses SAW technology

- 11 Cortex-M3 microcontroller cuts energy consumption

- 12 China's proposed ban of rareearth metals would affect hybrid cars, CFLs

- 12 Online-power-supply design tool evaluates 48 billion designs

- 13 Voices: Tim Draper: flowing venture capital where it's needed

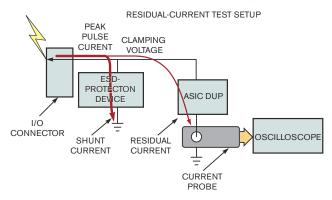

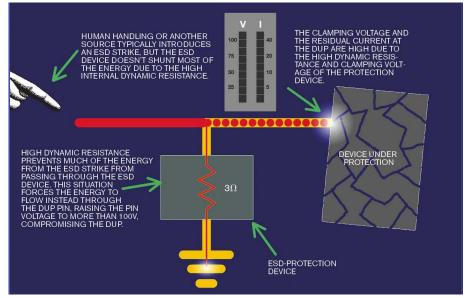

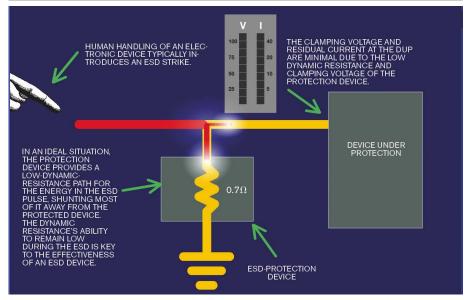

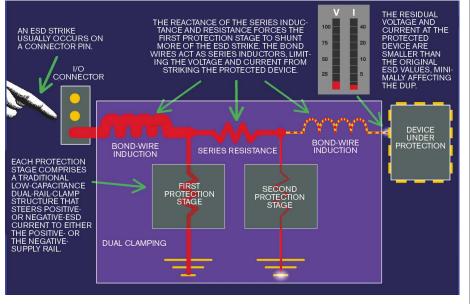

#### Evaluating ESD-protection components: Clamping voltage and dynamic resistance are crucial

**33** A changing product landfor improved protection against ESD strikes on components. A low-voltage device doesn't necessarily have greater protection. Protection comes from low clamping voltage and low dynamic resistance. by Chi T Hong, California Micro Devices

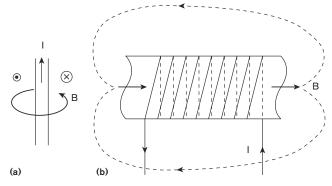

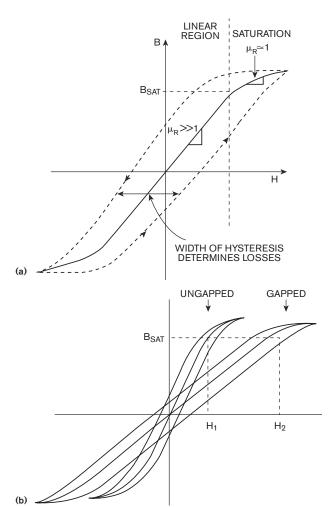

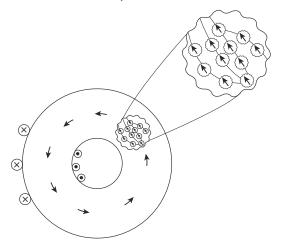

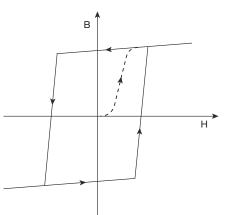

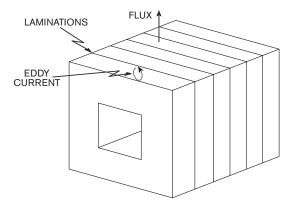

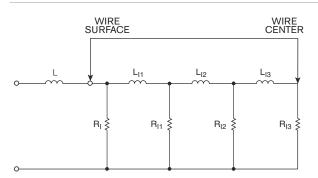

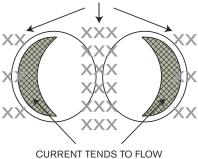

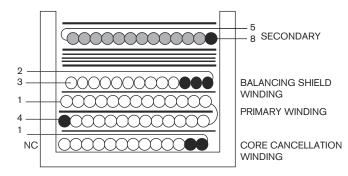

#### What every designer should know about magnetics in switchmode power supplies

36Power is often an afterthought in system design, but the choice and design of the magnetic elements at the heart of an SMPS are crucial. Acquaint or reacquaint yourself with the fundamentals of this frequently overlooked area.

> by Sameer Kelkar, Power Integrations

# DESIGNIDEAS

42 Inspect solar cells without a microscope

43 Solar-powered sensor controls traffic

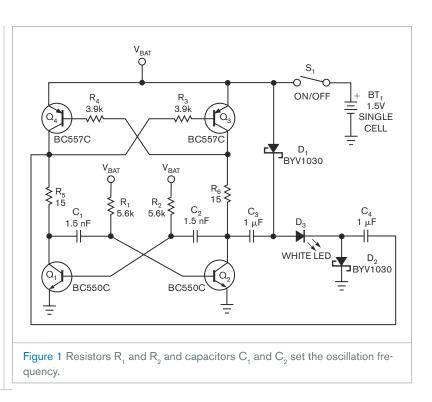

46 Self-oscillating H bridge lights white LED from one cell

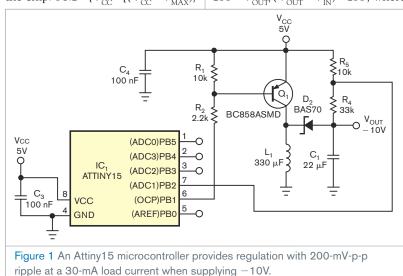

48 Low-cost LCD-bias generator uses main microcontroller as control IC

# How to pick the perfect inductor for your LED driver application

IC reference designs are a good start. But what if you want to optimize the driver inductor for size, efficiency or price?

Or evaluate newer, high performance parts that weren't available

when the reference design was created? Then you'll want to check out the new

Our new LED Design Center lets you:

- ✓ Search by IC to find all matching inductors

- Compare DCR, current rating, size and price

Analyze all core and winding losses

- Request free evaluation samples

- www.coilcraft.com/LED

LED Design Center on the Coilcraft web site. It's filled with interactive tools that let you compare hundreds of inductors for all LED driver topologies, including SEPIC.

To start your search for the perfect LED driver inductor, mouse over to www.coilcraft.com/LED

Coilcraft

# The Newest Optoelectronics

ORTEK KINGBRIGHT

#### **New Products from:**

Avago ASMT-Jx1x 1W Mini Power LED Light Source www.mouser.com/ avago1wminiled

#### LedEngin, Inc.

40W LED Emitter www.mouser.com/ ledengin40w

LUMEX

QuasarBrite™ Narrow Beam LEDs www.mouser.com/lumex\_ quasarbrite

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 390 leading suppliers.

a tti company

The Newest Products For Your Newest Designs

OSRAM **Opto Semiconductors**

IR OSTAR® Infrared LEDs www.mouser.com/ osramirostar

www.mouser.com **Over A Million Products Online**

PACIFIC SILICON SENSORS

3M TOUCH SYSTEMS

# **contents** 11.26.09

### **DEPARTMENTS & COLUMNS**

- **EDN.comment:** Weak economy, anti-immigrant sentiment hit H-1B visa program

- 4 Baker's Best: Understanding CMR and instrumentation amplifiers

- 16 **Prying Eyes:** Visionaire Lighting's Solar Vision Pole: shedding light on off-grid lampposts

- 50 Product Roundup: Optoelectronics/Displays

- 52 **Tales from the Cube:** Hawk eyes, analog equipment trump expensive digital test set

### **EDN** online contents

#### www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles: Specify an external reference clock to improve SERDES performance Various serial data standards require different clock specifications. →www.edn.com/article/CA6703242

#### Oscilloscope probe accessories-It's the little things that matter

Probe accessories, including tips, caps, adapters, springs, positioners, clips, and hooks, can help you conveniently make accurate measurements.

→www.edn.com/article/CA6704367

#### INNO ATION VANTED NOW!

Nominations for the 20th annual Innovation Awards www.edn.com/innovation

#### WHAT'S UP AT EDN.COM

#### Visit www.edn.com and

Sign up for our free newsletters or to receive your subscription digitally

Check out our Hot Topics to get all the information you need about what's HOT right now

• Check out the **News Center**, which provides up-to-the-minute news, analysis, research, and insight on the global electronics industry

• Check out the **Design Centers**, which feature articles, new-product information, and valuable design resources in several areas

and much, much more!

EDN ® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345, Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US; Jeff DeBalko, President, Business Media; Jane Volland, Vice President, Finance. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN ® copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year; (includes 7% 6ST, GST#12337457); Mexico, \$229.99 one year; air expedited, \$33999 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 54, Number 22 (Printed in USA).

# Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

| P | FC | " P | FC | ; |  |

|---|----|-----|----|---|--|

|   |    |     |    |   |  |

| Part<br>Number     | Pckg.         | V <sub>cc</sub><br>(V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |  |

|--------------------|---------------|------------------------|----------------|-----------------------|-----------------------------------|-----------------|--|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22                  | 50-200         | 1.5                   |                                   | ССМ             |  |

| /                  |               |                        |                |                       |                                   |                 |  |

#### SmartRectifier<sup>™</sup> IC

| ľ | Part<br>Number                 | IR1166S<br>PbF | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |  |  |  |  |

|---|--------------------------------|----------------|-----------------|-----------------|----------------|--|--|--|--|

|   | Package                        | S0-8           |                 |                 |                |  |  |  |  |

|   | V <sub>cc</sub> (V)            | 20             |                 |                 |                |  |  |  |  |

|   | V <sub>fet</sub> (V)           |                | <=200           |                 |                |  |  |  |  |

|   | Sw Freq.<br>max (kHz)          |                | 500             |                 |                |  |  |  |  |

|   | Gate Drive<br>±(A)             | +1/-4          | +2              | +1/-4           |                |  |  |  |  |

|   | V <sub>gate</sub> Clamp<br>(V) | 10.7           | 10.7            | 10.7            |                |  |  |  |  |

|   | Min. On Time<br>(ns)           | P              | 750             |                 |                |  |  |  |  |

|   | Channel                        | 1              |                 |                 | 2              |  |  |  |  |

|   | RoHS                           |                |                 | ~               |                |  |  |  |  |

For more information call 1.800.981.8699 or visit

International **ICR** Rectifier THE POWER MANAGEMENT LEADER

EDN.COMMENT

#### BY RICK NELSON, EDITOR-IN-CHIEF

# Weak economy, anti-immigrant sentiment hit H-1B visa program

he woeful employment picture in the United States is resulting in thousands of unfilled spots in the H-1B visa program for the first time since 2003, according to a recent article in The Wall Street Journal (Reference 1). Although employers in just one day snapped up all 65,000 available visas, would-be immigrants filed only 46,700 petitions for employment as of

Sept 25—about six months after employers scooped up the visas.

The article notes that, in addition to the weak economy, rising anti-immigrant sentiment in Washington and the higher costs of hiring foreign-born workers are also taking their toll on the visa program. Indian outsourcing companies such as HCL have traditionally been the largest recipients of H-1B visas, according to the article, but HCL has been hiring Americans who otherwise may have faced layoffs from companies switching work to HCL.

Would-be immigrants are also finding more opportunities at home. The article quotes Vivek Wadhwa, a scholar who has studied H-1B visas, as saying, "The best and the brightest who would normally come here are saying, 'Why do we need to go to a country where we are not welcome, ... our quality of life would be less, and we would be at the bottom of the social ladder?""

I commented on the trend for foreign nationals to stay home when I reported on a study Wadhwa conducted for the Ewing Marion Kauffman Foundation (references 2 and 3). The study notes that immigrant-founded US-based companies employed 450,000 workers and generated \$52 billion in revenue in 2006. The WSJ article quotes Microsoft general council Brad Smith as saying that 35% of Microsoft's US patent applications last year came from new inventions by visa and green-card holders.

"While some have tried to associate the increase in foreign workers ... with the economic problems that have plagued the country, this data verifies the opposite effect," said Wadhwa when the Kauffman Foundation released its study. "If the US government and the business community could find better ways to offer good jobs in tandem with less restrictive visa policies for talented immigrants, the United States might be able to recapture many of these immigrants and their potential to help grow the US economy."

Companies such as Microsoft that benefit from the visa program VIELD contend that the current slump in the program demonstrates that the market, not Congress, should determine how many immigrants should be allowed to work in the United States. The WSJ article quotes Jenifer Verdery, director of work-force policy at Intel, as saying that the fact that the cap hasn't been reached this year shows that the market will temper demand.

There seems to be bipartisan disagreement in Congress with that position. As the WSJ reports, Senator Charles Grassley, an Iowa Republican, wrote a letter to the new director of citizenship and immigration services, urging tighter controls on H-1B visas. In April, Grassley and Illinois Democrat Senator Richard Durbin introduced legislation to require companies to pass more stringent labor-market tests that would ensure they make a bigger effort to hire US workers.

The H-1B visa program is valuable, and, as the Kauffman Foundation study points out, immigrants have contributed disproportionately to the US economy's high-tech sector. If Americans are unwilling or unable to contribute their fair share, then it will be important to US economic success to attract talent from overseas. There is a role for Congress to play to provide further safeguards so that cheaper workers from abroad don't displace motivated, qualified Americans. If Congress can ensure Americans that the program works as intended, political support for expanding the program might grow.EDN

#### REFERENCES

Jordan, Miriam, "Slump Sinks Visa Program," The Wall Street Journal, Oct 30, 2009, http://online.wsj.com/article/ SB125677268735914549.html. Nelson, Rick, "Immigrant brain-drain challenges US innovation," Test & Measurement World, March 2, 2009, www.edn.com/091126eda. Wadhwa, Vivek, et al., "America's

Loss is the World's Gain," Ewing Marion Kauffman Foundation, March 2009, www.kauffman.org/uploaded files/americas loss.pdf.

Contact me at rnelson@reedbusiness. com.

#### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617; judy.hayes@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

> SENIOR ART DIRECTOR Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor

1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

NEWS Suzanne Deffree, Managing Editor 1-631-266-3433;

sdeffree@reedbusiness.com

POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Web Operations Specialist 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

EDN EUROPE Graham Prophet, Editor, Reed Publishing +44 118 935 1650;

gprophet@reedbusiness.com **EDN ASIA** Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com

Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

> EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-8551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag. com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# **NAXING RELIABILITY** In contact, stability and low noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance

- through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

#### Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

MILL-MAX

www.mill-max.com/EDN596

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

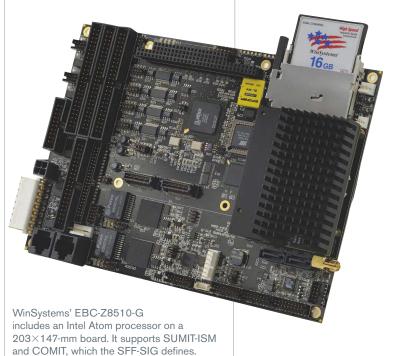

### WinSystems highlights Atom board, CompactFlash

Www.sff-sig.org) defines.

The \$795 EBC-Z530-G includes an array of onboard peripherals and expansion options. It uses either a 1.1-GHz or a 1.6-GHz Atom and the SCH (system-controller hub)-US15W with 512 Mbytes or 1 Gbyte of DDR2 system memory. The EBC-Z510-G's I/O interface features two GbE (gigabit-Ethernet) ports, CRT and LVDS (low-voltage-differential-signaling) flat-panel video, a MiniPCIe (Peripheral Component Interconnect Express)-card interface for a wireless-networking module, four USB (Universal Serial Bus) 2.0 ports, four serial COM ports, HD (high-definition) audio, a PATA (parallel-advanced-technology-attachment) controller for both a CompactFlash and a hard disk, 48 lines of digital I/O, a parallel printer port, and a PS/2 port. Two SUMIT and legacy PC/104 connectors support additional I/O-module expansion. The ROHS (reductionof-hazardous-substances)-compliant board operates over an industrial temperature range of -40 to +70°C for processor- and I/Ointensive applications in harsh environments.

Because the EBC-Z510-G's architecture is PC-compatible, it supports Windows XP embedded and Linux operating systems along with a software-development tool set that includes device drivers and libraries. It also supports advanced features, such as a custom splash screen, APM (advanced-power-management) and ACPI (advanced-configurationand-power-interface) modes, and PXE (preboot execution environment).

According to WinSystems' vice president, Robert Burkle, the EBC-Z510-G is the first board to support COMIT, which targets use in SFF processor modules and baseboards. The company uses a  $62 \times 75$ -mm SFF-COM card, which is roughly the size of a credit card, that includes the Atom, SCH, memory, and power supplies. For more on this introduction, go to www.edn.com/article/CA6699174.

#### -by Rick Nelson

**>WinSystems**, www.winsystems.com.

#### FEEDBACK LOOP "The debunker dog in you should get busy. ... If I'm wrong I'll eat my words (or breathe the fumes—whatever)."

-Engineer Meredith Poor, in EDN's Feedback Loop, at www. edn.com/article/CA6670951. Add your comments.

# pulse

# High-performance MSOs feature 20-GHz analog bandwidth

ektronix has announced the MSO70000 series of MSOs (mixed-signal oscilloscopes). The instruments can capture as many as 20 channels of data–four analog with bandwidth ranging from 4 to 20 GHz, depending on the model, and 16 digital with timing resolution of 80 psec on all models. Memory depths to 250M points are available on all channels of all models.

The MSO70000 combines a full suite of measurement capabilities that help resolve analog issues in digital systems. You can use the instruments to debug and verify in such demanding, high-speed design applications as DDR memory, highperformance ASICs, FPGAs, SOCs (systems on chips), and digital RF. The MSO70000 offers a variety of probing accessories for making minimally disruptive analog and digital connections to a DUT (device under test).

The instruments deliver advances in the discovery of problems, capture of notable events, quick searches through long records to reveal the captured events, and analysis to obtain rapid insight into the causes of anomalous DUT behavior. The devices offer as much as five times the bandwidth and timing resolution of the fastest-avail-

On each of their four analog channels, MSO70000 series instruments offer five times the bandwidth of other MSOs. Each of the 16 differential-input digital channels provides 80-psec timing resolution and up to 250M samples of capture memory.

able integrated MSOs.

Maximum sample rates are 50G samples/sec on analog channels and 12.5G samples/ sec on digital channels. To minimize confusion, the analog- and digital-record durations always match; the scopes add repeated samples to the channels that are acquiring at the lower rate so that analog and digital records always contain equal numbers of samples. This feature allows you to capture longduration events with high sample resolution and obtain timecorrelated views of high-speed analog and digital data.

The MSO70000 series provides a comprehensive set of innovative solder-in probe accessories that simplify connecting to vias and fine-pitch components on tightly packed boards to acquire such signals as those on the digi-

**DILBERT By Scott Adams** SATAN'S VENDOR FOR EXAMPLE, WHEN YES. DO YOU YOU'LL HAVE MANY ONE OF OUR PRODUCTS THEY'RE STOPS WORKING, WE'LL HAVE MADE OF BENEFITS AFTER OUR BLAME ANOTHER FREE THE FINEST TECHNOLOGY IS VENDOR WITHIN 24 T-SHIRTS? ALLERGENS. IRREVOCABLY HOURS. IMPLEMENTED IN YOUR ww.dilbert.com NETWORK,

tal-control lines of the DDR command bus. The tool set for DDR probing now also includes new BGA interposers for all variants of DDR3- and DDR2-memory components and provides access to all signals with excellent fidelity. The units work with the company's iCapture technology, which allows internal routing of selected digital signals to the analog channels for full analog evaluation, making the MSO70000 ideal for highly sensitive, finepitch board layouts.

The iCapture feature offers analog views of any connected digital channel, providing debugging insight across all 20 channels. The series provides serial-pattern, mixed analog and digital, logic-pattern, and bus-state triggers, which you can combine to isolate system faults that occur only during particular system states. The units provide tight timing synchronization between the analog and the digital subsystems. Timing correlation as close as 80 psec is possible, resulting in easier determination of the cause and effect of circuit behavior.

More than 30 analysis suites run on the series. You can select from the new I<sup>2</sup>C (inter-integrated-circuit) and SPI (serial-peripheral-interface) busanalysis tools, DPOjet (digitalphosphor oscilloscope jet) for jitter and eye-diagram analysis, DDRA (DDR analysis) for DDR-memory-bus verification, SDLA (serial-data-link analysis) for equalized-channel emulation and analysis, and SignalVu for frequency-domain display and analysis. The manufacturer's suggested US retail prices for the MSO70000 units start at \$67,400.

−by Dan Strassberg **Tektronix Inc**, www. tektronix.com.

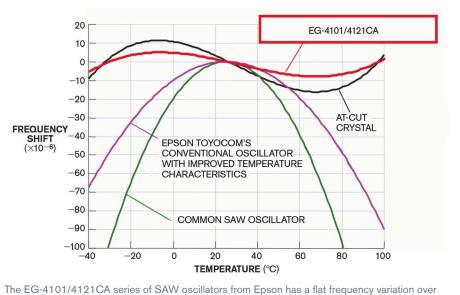

### Stable quartz oscillator uses SAW technology

argeting LANs (localarea networks) and SAN (storage-area networks), Epson Toyocom recently announced the highly stable EG-4101/4121CA SAW (surface-acoustic-wave) resonator. The part combines low jitter, low phase noise, high stability, and temperature coefficients better than those of AT-cut

temperature.

quartz crystals. The resonator offers a frequency tolerance of  $\pm 50$  ppm and maximum phase jitter of 0.2 psec at 622 MHz over a 12-kHz to 20-MHz bandwidth. The device is available with LV-PECL (low-voltage-positive-emitter-coupledlogic), LVDS (low-voltage-differential-signaling), and HCSL (high-speed-current-steer-

ing-logic) outputs. Available frequency ranges are 100 to 700 MHz for the LV-PECLand LVDS-output versions and 100 to 500 MHz for the HCSL version. The resonator has a supply voltage of 2.5 to 3.3V, and current consumption ranges from a maximum of 30 or 45 mA over the supply-voltage range for the LVDS version

to 80 or 100 mA for the LV-PECL version.

SAW resonators and oscillators differ from SAW filters in that the resonators use a guartz rather than a ceramic element. Don't confuse SAW resonators with inexpensive silicon or ceramic resonators, which tend to have a much lower Q (quality factor) and worse initial accuracy and temperature coefficients. Because the SAW resonators operate at their fundamentalresonance mode, they lack the frequency jitter of conventional crystal oscillators that operate at a lower frequency; a PLL (phase-locked loop) then multiplies that frequency inside the chip. The operation at fundamental mode also means that the parts do not frequency-hop as quartz crystals do.

The EG-4101/4121CA device operates over a standard temperature range of -40 to +85°C or an optional range of -40 to  $+90^{\circ}$ C and comes in a  $7 \times 5 \times 1.2$ -mm package. It sells for \$12 to \$18 (1000) and is available for sampling now.

-by Paul Rako

epsontoyocom.co.jp/english.

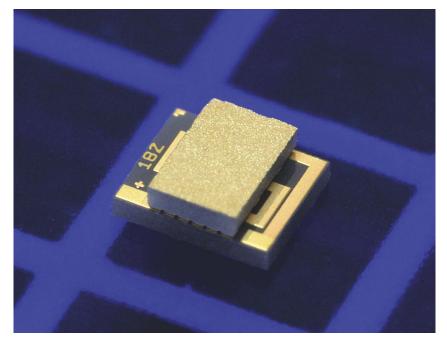

#### CORTEX-M3 MICROCONTROLLER CUTS ENERGY CONSUMPTION

Energy Micro's new EFM32G Gecko microcontroller family sports an energy-efficient implementation of a 32-bit ARM (www.arm.com) Cortex-M3-microcontroller architecture. The family thus targets applications, such as meters, requiring extended battery life. The devices support five power modes with an operating voltage range of 1.8 to 3.8V. Active-mode current consumption is as low as 180  $\mu$ A/MHz at 3V when executing code from flash memory. Standby current consumption is 900 nA at 3V with a real-time clock, a 32.768-kHz oscillator, power-on reset, brownout detection, and full RAM and CPU retention. Deep-sleep-mode current draw is 20 nA at 3V, and wakeup time from sleep mode is as fast as 2  $\mu$ sec.

The 32-MHz microcontroller configurations include as much as 128 kbytes of on-chip flash and 16 kbytes of RAM. Low-power components include a 200-µA, eightchannel, 12-bit, 1M-sample/sec ADC; a 100-nA brownout

detector; a 50-nA, 32-kHz real-time counter; a 100-nA-receive-mode, 9600-bps-capable UART; and a 50-nA watchdog timer with dedicated RC oscillator. The ADC supports single-ended or differential operation. The 12-bit, 500ksample/sec DAC supports two single-ended channels or one differential channel. As many as two analog comparators are available with support for capacitive sensing with as many as eight inputs. As many as 90 GPIOs (general-purpose input/outputs) support a 20-mA drive strength. Hardware AES (Advanced Encryption Standard) with 128/256-bit encryption and decryption is available. The configurable LCD controller can drive an array of 4×40 segments.

Prices for the 32-pin devices start at \$1.55 (100,000). For more details on this series, go to www.edn.com/ article/CA6704374.-by Robert Cravotta Energy Micro, www.energymicro.com.

**Epson Toyocom**, www.

# pulse

# China's proposed ban of rare-earth metals would affect hybrid cars, CFLs

hina's Ministry of Industry and Information Technology is proposing a total ban on exports of terbium, dysprosium, yttrium, thulium, and lutetium and a restriction on neodymium, europium, cerium, and lanthanum to a total of 35,000 tons a year, which is far below global needs. Many of these metals are vital to energy-efficient technology. For example, neodymium finds use in rare-earth magnets for high-efficiency motors, and new front-loading clothes washers use rare-earth magnets in their motors.

According to a recent article (**Reference 1**), "No replacement has been found for neodymium that enhances the power of magnets at high heat and is crucial for hard-disk drives, wind turbines, and the electric motors of hybrid cars. Each Toyota Prius uses 25 pounds of rare-earth elements. Cerium and lanthanum are used in catalytic converters for diesel engines." Manufacturers use terbium in the phosphors of CFLs (compact fluorescent lights) to tweak their light to a more pleasant spectrum.

China is currently the only producer of some of these metals, so the country's restriction or banning of its exports will affect energy-efficient products worldwide. According to the article, China's Neodymium is crucial for hard-disk drives, wind turbines, and the electric motors of hybrid cars.

intent is not to hold the rest of the world hostage; China needs these metals for its internal consumption.

China put many global competitors in rare-earth minerals out of business in the early 1990s by flooding the market, leading to the closure of the biggest US rare-earth mine, in Mountain Pass, CA, which Molycorp Minerals operates. The mine is one of the world's largest and richest rare-earth deposits, and the company is producing a variety of green elements there. It plans to bring the facility back into full production and re-establish domestic manufacturing capacity.

-by Margery Conner Molycorp Minerals, www. molycorp.com.

#### REFERENCE

Evans-Pritchard, Ambrose, "World faces hi-tech crunch as China eyes ban on rare metal exports," *Telegraph*, Aug 24, 2009, www.telegraph.co.uk/ finance/comment/ambrose evans\_pritchard/6082464/ World-faces-hi-techcrunch-as-China-eyes-banon-rare-metal-exports.html.

#### ONLINE POWER-SUPPLY DESIGN TOOL EVALUATES 48 BILLION DESIGNS

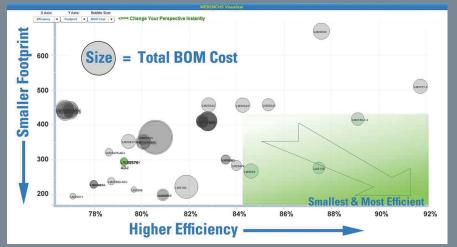

**National Semiconductor** has made significant improvements to its free Webench online-design tool, which operates with most popular Web browsers. You access the tool using a one-time transfer of a database in flash format to your computer. The tool provides a speedy response as you experiment with various design configurations. It includes the new Visualizer tool to chart efficiency, footprint, and cost variables. An optimizer dial lets you establish your preference for trade-offs among footprint, efficiency, and cost.

You set a dial that causes the tool to generate 50 to 70 designs from 48 billion combinations and to select from 25 power-supply topologies, including buck, boost, buck-boost, SEPIC (single-ended-primaryinductance converter), and flyback. The tool has a database of 21,000 components from 110 manufacturers and is suitable for designs with in-

put voltages of 1 to 100V, output voltages of 0.6 to 300V, and power as high as 300W. It can help you design for efficiency as high as 96% and switching frequencies as great as 3 MHz. The smallestfootprint design is 14×14 mm. Webench requires no registration until you run simulation or thermal analysis; at that point, you need to register for a user account to store the results.-by Paul Rako National Semiconductor, 11.26.09

www.national.com.

The improved Webench online-design environment has a visualization tool that lets you contrast the trade-offs of price, size, and efficiency in your power-supply designs.

### VOICES Tim Draper: flowing venture capital where it's needed

im Draper is managing director of venture capital at Draper Fisher Jurvetson (www.drapervc.com) and chairman of Bizworld (www.bizworld.org), a nonprofit organization that teaches entrepreneurship and business to children. *EDN* recently conducted an interview with him, a portion of which follows. You can read the complete interview at www.edn.com/091126pb.

# What is the fundamental trade-off between venture capital and private equity?

A Both are valuable parts of the financial markets. Venture capital invests in entrepreneurs who want to build companies from nothing. Private equity invests to make existing companies more efficient. Venture capital is usually around start-ups and technology. Private equity can be for any established company in any field.

#### Do you have some patriotic desire to fund entrepreneurs in the United States?

No. I fund entrepreneurs who want to change the world wherever they may be. In fact, America is driving them away. Technical immigrants on the whole create jobs for Americans. If companies in the United States become uncompetitive globally, we lose jobs.

#### Do you feel that philanthropic involvement is an important part of being successful?

A I mostly believe in the power of business to improve our lives. Most of my philanthropic activity has been around teaching and encouraging entrepreneurship globally.

#### Is regulation an essential part of a complex technological society?

Big government was as responsible as anyone for the crash. Fannie Mae and Freddie Mac guaranteed loans they shouldn't have. Banking regulators changed the Glass-Steagall Act, which encouraged banks and investment banks to merge. In addition, the Community Redevelopment Act created a market for risky subprime loans. You can't regulate good behavior. In fact, I would argue that a freer country has fewer criminals. Our government has gone from spending 8 to 40% of our GDP [gross domestic product] over the last 100 years. Our country in effect trusts itself less than it did. and it is killing our growth.

#### The liquidity crisis makes it harder for you to cash out with an IPO [initial public offering], but there must be massive amounts of idle capital available for you to invest.

sits in places where people can't trade it, so in effect there is less of it to use for new investments. In our case, our limited partnerships invested their money with us. We then invested that money in tech start-ups. Some of those startups grew and created jobs and wealth, but that wealth is sitting in illiquid companies that can't seem to get public, so there is no money to return to investors. Unless investors get money back, they can't invest in more companies. Liquidity allows flexibility and creates wealth.

#### Instead of spreadsheets, do you look for a story, one that anticipates all the twists and turns of a creative endeavor?

Of course. What we look for in an investment is a creative, enthusiastic chief executive officer, a motivated team, and a vision to take a unique technology to a very large global market.

### Why are you a proponent of global free trade?

A If the US government forces its businesses to use any workers who are not the best for the job, it will make the United States uncompetitive globally, which will make the entire country poorer and have the effect of making the United States lose more jobs and so on until there is no business left here.

#### Tell us about the stock market you are attempting to create.

Expensive regulation now costs companies on the order of \$3 million a year and has made it untenable for a business that earns less than \$10 million a year in profit to go public. Xchange is a new private market that allows companies to "go private" and be traded before they are big enough to go public.

#### Do the business plans of all your start-ups have an IPO as an exit strategy, or is a buyout perfectly acceptable?

I am not as fond of buyouts because they limit the upside of a company's potential, and they normally lose jobs. Also, since we are always looking for companies that will define and create industries, an acquisition can keep a new industry from forming. The IPO was a great alternative that allowed a company's shareholders to trade shares without losing the company's focus or general direction. Now, however, IPOs are too expensive for most companies that would like to get liquidity for shareholders, so we started Xchange to allow companies some liquidity for shareholders without spending all the money required to comply with expensive regulations, such as Sarbanes-Oxley.

What's the most promising company you are funding?

-interview conducted and edited by Paul Rako

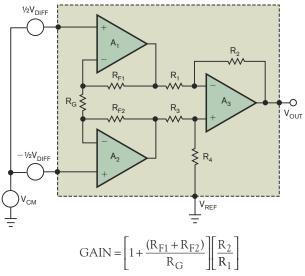

# Understanding CMR and instrumentation amplifiers

he three-op-amp instrumentation amplifier in **Figure 1** is seemingly a simple configuration in that it uses a basic, decades-old operational amplifier to gain a differential input signal. The op amp's input offset-voltage error is easy to understand. The definition of an op amp's open-loop gain has not changed. The simple idea of an op amp's CMR

(common-mode rejection) has been around since the beginning of op-amp time. So what is the hang-up?

**Equation 1** yields the common CMR for a single op amp and instrumentation amplifier:

$$\mathrm{CMR} = 20\log \frac{G \times \Delta V_{\mathrm{CM}}}{\Delta V_{\mathrm{OUT}}}, \qquad \text{(1)}$$

where G is the system gain,  $\Delta V_{CM}$  is the changing common-mode voltage that you apply equally to the system's input terminals with respect to

Figure 1 In this three-op-amp instrumentation amplifier, V<sub>CM</sub> is the common-mode voltage, and V<sub>DIFF</sub> is the differential input to the same instrumentation amplifier.

the relationship of these resistors:

$$CMR_{A3} = 20 \log \left[ \frac{100 \times (1 + R_2 / R_1)}{\% ERROR} \right]$$

. (2)

For instance, if  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are approximately the same value and the ratio of  $R_3$  to  $R_4$  is 1.001 of  $R_1/R_2$ , this 0.1% mismatch will cause a degradation of the instrumentation amplifier's CMR from ideal to a 66-dB level. At a gain of one, CMR<sub>A3</sub> is equivalent to the CMR of the entire instrumentation amplifier.

As Equation 1 states, the instrumentation amplifier's CMR increases as the system's gain increases-a nice feature. Equation 1 might motivate an instrumentation-amplifier designer to ensure that there is plenty of gain available, but A1 and A2's open-loop gain error places a limit on this strategy. An amplifier's open-loop gain is  $20\log(\Delta V_{OUT}/\Delta V_{OS})$ , where  $V_{OS}$  is the offset voltage. As the gain of A<sub>1</sub> and  $A_2$  increases, the offset errors from the amplifier's open-loop gain also increase. The changes in output swing of  $A_1$  and  $A_2$  typically span the supply rails. At higher instrumentation-amplifier gains, the open-loop gain error of the op amps dominates. These errors degrade the CMR of the instrumentation amplifier at higher gains. Consequently, the instrumentation amplifier's CMR performance values tend to reach a maximum value at higher gains.

So, from the CMR perspective, instrumentation amplifiers are systems in which various parts contribute to the CMR error at different system gains. This situation is not so mysterious when you think about the inside of this device. As you separate the parts, the picture becomes clear.EDN

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie@ti.com.

ideally infinite.

ground, and  $\Delta V_{_{\rm OUT}}$  is the change in

the system's output voltage with re-

the op amp are straightforward; the

change of offset voltage is the only concern. Two factors influence an in-

strumentation amplifier's CMR. The

first and most dominant factor is the

balance of the resistor ratios across

$A_3$ . For instance, if  $R_1$  equals  $R_3$  and

$R_{\lambda}$ , equals  $R_{\lambda}$ , the CMR of the three-

op-amp instrumentation amplifier is

With CMR, the inner workings of

spect to the changing  $V_{CM}$  values.

At a real-world level, however, the relationship of  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  to the instrumentation amplifier's CMRspecifically, matching the  $R_1$ -to- $R_2$ ratio to the R<sub>3</sub>-to-R<sub>4</sub> ratio—is critical. These four resistors combine with A, to subtract and gain the signals from the outputs of A1 and A,. A mismatch between the resistor ratios creates an error at the output of A<sub>3</sub>. Equation 2 gives the contribution to the CMR error with respect to

14 EDN | NOVEMBER 26, 2009

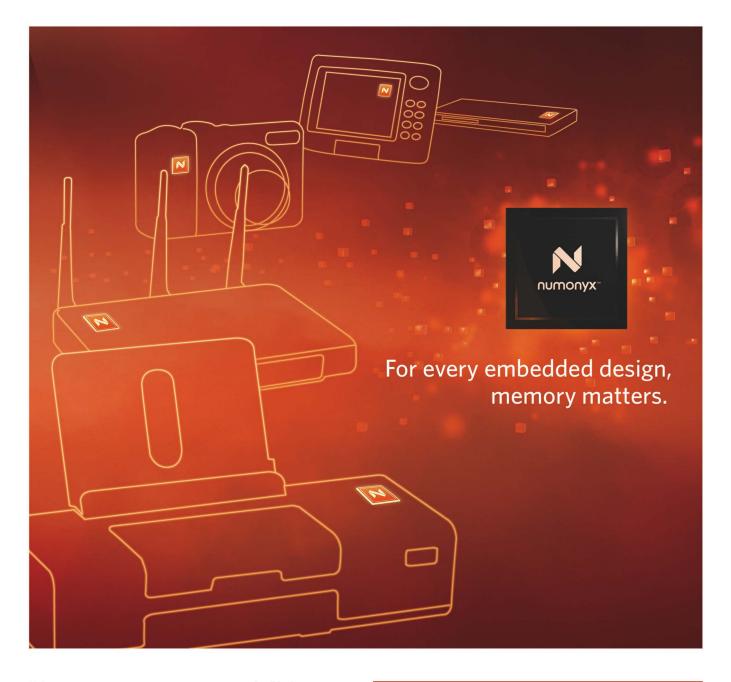

When it comes to creating your next embedded system, an important decision awaits you. Memory. Your design needs speed, reliability, performance and capacity to store the code and data your design demands. No problem. Numonyx has the broadest portfolio of parallel and serial NOR, NAND and phase change memory. And we offer extended temperature support with AEC-Q100 certification on many of our products and expanded design versatility with voltage support up to 5V. All designed to deliver a right-fit solution to help you shorten design cycles, reduce development costs and accelerate the roll-out of your next big idea. Find out how Numonyx memory matters for your next design.

Visit www.Numonyx.com/Embedded for free access to the Numonyx Embedded Design Center.

#### <u>NUMONYX® FORTÉ™ SERIAL</u> FLASH MEMORY

| Product Family           | Density Range  | Voltage/Solution |  |

|--------------------------|----------------|------------------|--|

| M25P (block erase)       | 512 k - 128 Mb | 3V, single-I/O   |  |

| M25PX (4KB block erase)  | 4 Mb - 64 Mb   | 3V, multi-I/O    |  |

| M25PE/M45PE (page erase) | 1 Mb - 16 Mb   | ЗV               |  |

#### NUMONYX® AXCELL™ PARALLEL NOR FLASH MEMORY

| Product Family                                | Density Range | Voltage/Solution |

|-----------------------------------------------|---------------|------------------|

| M29W/EW (JEDEC command set)                   | 4 Mb - 2 Gb*  | 3V, page read†   |

| P30/33 (Intel-based command set, sync burst): | 64 Mb - 2 Gb* | 1.8/3V core      |

#### **PRY FURTHER AT EDN.COM**

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

# Visionaire Lighting's Solar Vision Pole: shedding light on off-grid lampposts

espite the high light efficacy of HB LEDs (high-brightness light-emitting diodes), their cost for commodity applications is still too high for them to compete head-on with older forms of lighting, such as incandescent and HID (high-intensity-discharge) lights. However, certain applications can justify paying a premium for high efficiency, long life, ruggedness, and light-color-temperature control, and these applications represent the sweet spot for HB LEDs.

One such application is solar-powered outdoor lighting for off-grid applications. Visionaire Lighting's Solar Vision Pole lamppost is especially novel because it does not use a standard rigid solar panel that requires additional bracing for wind shear and can attract the attention of scavenging thieves. Instead, a flexible solar panel encases the post and charges four gel batteries in its base. The size of the panel and the number of batteries limit the lighting to 50W, which is a weak traditional light source but makes for a strong, white-LED light. Six hours of charging is enough to run the light all night.

The amorphous-silicon flexible Solar Flex cells produce uni-

form power even as the sun's rays hit the round column of cells at an angle, easing the power-management task for the post. For lighting applications requiring 100 to 125W of power, the post is available in a version with a flat-mount polycrystalline panel that is both larger and more efficient than the other version. The Aria-model light fixture has 48 Philips Lumiled HB LEDs. Visionaire chose these devices because they provide 100 lumens/W over a wide color-temperature range. Some HB LEDs can provide 100 lumens/W but only at a blue shade of white, typically a blue-white 6500K. Blue-white-colored lights can contribute to night-sky light pollution, which is the bane of observatories and dark-sky protectors.

The four gel-type battery packs in the lamp base can provide as much as 50W to the LEDs. The 12V-dc batteries each offer 30.5 Ahr. A full charge supports 40 hours of continuous illumination. The light operates at ambient temperatures as low as  $-76^{\circ}F$ . Agilent

Tektronix

LeCroy

**Rohde & Schwarz**

**National Instruments**

Anritsu

Keithley

Yokogawa

Tabor

**Pickering**

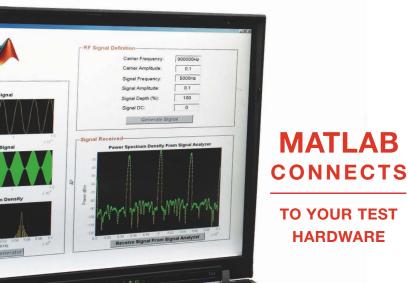

**MATLAB**

**TO YOUR TEST** HARDWARE

LX 000 00 (4.5p 01 Full Screen <u>ि</u> (७। SIGNAL ANALYZER 20 Hz ... 26.5 GHz HDE&SCHWARZ FSQ REH 1 HHz 5

> Connect to your test equipment directly from MATLAB® using standard communication protocols and hundreds of available instrument drivers.

Analyze and visualize your test results using the full numerical and graphical power of MATLAB.

For more information on supported hardware, visit www.mathworks.com/connect

© 2009 The MathWorks. Inc. MATLAB is a registered trademark of The MathWorks, Inc. Other product or brand names may be trademarks or registered trademarks of their respective holders.

LXI

GPIB

IVI

TCP/IP

VISA

**USB**

UDP

**RS-232**

CHIP DESIGNERS' STRUGGLES TO PROVIDE TRIPLE-PLAY HD SERVICE TO TELEPHONE, CABLE, AND WIRELESS CUSTOMERS ARE CHANGING THE NATURE OF SOC ARCHITECTURE.

BY RON WILSON . EXECUTIVE EDITOR

he forces converging on the telecom and networking businesses have their roots in the changing desires of end users, and changing traffic patterns reflect those desires. For home-computer users, the mostly one-way HTML (hypertext markup language) traffic of Web browsing is gradually evolving into a rich mix of HTML, compressed HD (high-definition) video, interactive high-resolution graphics, and latency-intol-

erant HD audio. The heavily asymmetric traffic of Web browsing is becoming the more symmetric traffic of peer-to-peer networking.

Nowhere are these changes happening faster or with more public results than in the cellular-access networks, which are struggling to support new smartphones, such as the iPhone.

Mike Coward, chief technology officer at Continuous Computing, points out that mobile-broadband data traffic is doubling every nine months. "The iPhone does 30 times the traffic of a conventional handset," Coward says. "But that's not the bad news. Netbook users appear to create 450 times the traffic of handsets. All the operators are running up against spectrum limitations."

The iPhone is not the end of the story, either. Handset designers are pressing ahead with plans for mobile devices that can display and capture HD video. "Even with LTE [long-term evolution], there's not enough air bandwidth to give everyone HD video in their palm," Coward says. And a movie viewer in every palm is not the worst-case scenario. "Peer-to-peer traffic from netbooks and video sharing can be network breakers," he warns.

Mobile services must live within the physics of their air interfaces and thus face the most acute problem. Even cableand telephone-service providers are under pressure, however. "While US-based broadband customers game, e-mail, and social-network over 384-kbps or 3-Mbps links, our counterparts in Korea, China, or Japan are real-time gaming and sharing video on 40- to 100-Mbps links," says Bruce Tolley, vice president of corporate marketing at Solarflare Communications. "A common deployment in Japan and China is IEEE 802.3ah PON [passive-optical-network] fiber to the building, with 100-Mbps VDSL [very-high-speed-digital-subscriber-line] tails into the houses. This [bandwidth] is more than many of us have available in our corporate networks here in the United States."

So US cable and telephone operators are scrambling to upgrade, driving optical fiber as close as possible to the customer premises and then bridging the so-called last mile with cable or twisted pairs. "Cable operators will be strong in triple-play [voice, data, and video] in the United States," says Greg Fisher, vice president and general manager of Broadcom's carrier-access business. "With new VDSL technology, the telephone-company operators should be able to provide 50 to

A new generation of silicon architectures is rising to the challenge.

100 Mbps on their copper for short distances." That ability is a big deal for the carriers. Verizon believes it can charge more than \$100 per user per month for that kind of service. So nearly everyone is in the same boat. Sooner or later, bandwidth limitations will keep customers from using the network as they wish.

Security is yet another issue lurking beneath the surface of the shift in network use. Network-application providers, ISPs (Internet-service providers), and carriers all must protect themselves from denialof-service attacks and intrusion. And carriers must protect their subscribers. "People are not talking enough about mobile security," Coward warns. "The first time there is a big intrusion into smartphones, users are going to blame their carriers." The same argument could apply just as well to fixed-service providers.

#### **A NOSIER, SMARTER NETWORK**

According to networking experts, the solutions to both of these problems—

Figure 1 Xelerated's HX330 is an evolution of the programmable-pipeline strain of architectural thinking.

running out of bandwidth and securitybegin in the same place: with knowing what is in the packets traversing the network. To make the most of what bandwidth they have, carriers must shape the traffic that passes through their domains. And to protect themselves and their customers, carriers and service providers must identify and destroy pernicious packets. Both of these processes require inspection of the packets as they pass through switches, routers, and even, some argue, line cards. But where to perform this inspection, how deeply to look into the packet, and what to do with the resulting information are all debated issues, the resolutions to which are greatly influencing silicon design.

"Bandwidth gets very expensive in access networks," says Kent Fisher, chief systems engineer at Freescale Semiconductor. "So there is a lot of incentive for carriers to parse the packet stream, identify the applications that are using the packets, and apply protocols and traffic shaping to get the most out of their bandwidth."

DPI (deep packet inspection)—looking deep enough into a packet to identify its payload—has many attractions. DPI allows a switch or router to prioritize and schedule individual packets—for example, giving latency-intolerant audio packets an immediate departure, making

sure that the packet stream for an HDvideo player gets its required minimum bandwidth, and scheduling HTML packets for a browser before data packets for a file swap. And detecting virus-bearing or denial-of-service traffic can also require looking at the payload. More controversial is the revenue aspect of the question. DPI allows a carrier to identify and charge extra for packets associated with premium services or to impede packets from rival services. Other issues surround DPI, as well. If packets are encrypted and you can get the key, then inspection requires decrypting and re-encrypting each packet. "About half the time, there is no way to read encrypted traffic, so you have to rely on statistical techniques to guess what the packets are," says Continuous Computing's Coward.

And DPI is hard work. Instead of just breaking apart the header on each packet, you have to read the whole thing and, in the worst case, run it through a regular-expression processing algorithm to detect embedded patterns that can indicate data types or the presence of a virus. Particularly in software, that task takes a lot of cycles and a lot of energy. "With all of their requirements, mobile operators are asking us for 20 times more processing work per packet than in yesterday's systems," Coward says.

#### **WHO DOES THE WORK?**

Who will do all this work is another difficult issue. "Classification and QOS [quality-of-service] processing have to happen from end to end of the network, even in the metro networks," says Freescale's Fisher.

"You don't want to end up doing deep classification at really high bit rates," however, says Syed Shah, a systems architect at the company. "It's much more

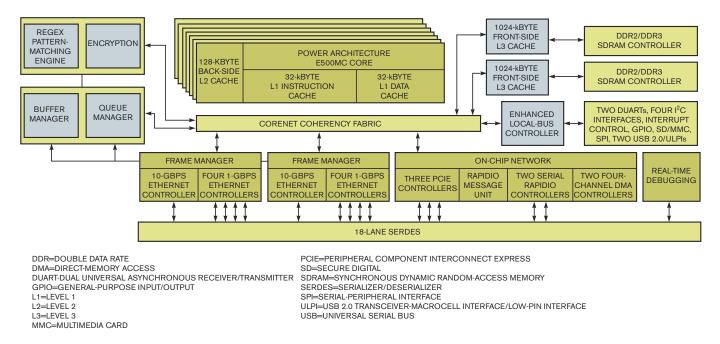

Figure 2 Freescale's 4080 family processors bear a family resemblance to other heterogeneous multicore-processor architectures.

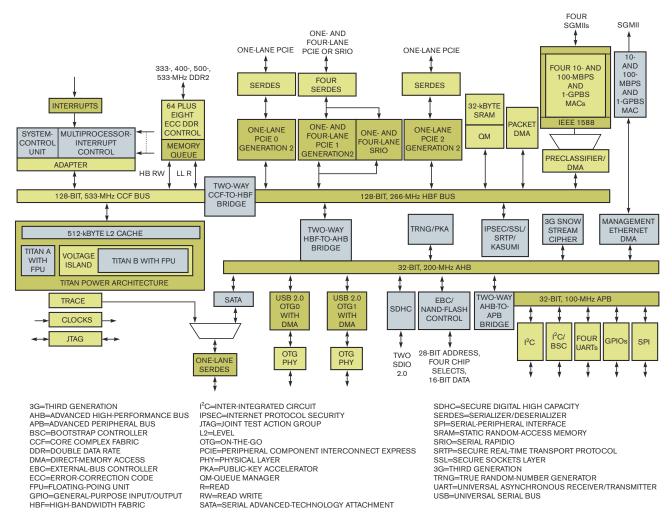

Figure 3 Applied Micro's chip architecture resembles nothing so much as the architecture of the networks in which it will find use.

feasible to inspect the packets in the access network." Network architects recognized this situation years ago and came up with ideas such as MPLS (multiprotocol label switching) and the QOS bits in the IPv4 (Internet Protocol Version 4) header. In these schemes, a classification engine inspects each packet at or near its source and leaves a marker at Layer 2 or 3, indicating the priority the packet requires. Switches and routers deeper in the network then need not perform deep inspection.

"We see businesses trying to aggregate data and voice traffic from multiple ISPs and to route the packets using QOS bits or VLAN [virtual-local-area-network] tags," says Michael Durant, vice president of engineering at Arcturus Networks. This approach can in principle keep most of the switching decisions at Layer 2. "But browser vendors compete with each other on things like audio quality," Durrant continues. "So they routinely set the QOS bits very high. That practice creates artificially stringent QOS demands."

Even with all applications playing fairly, legitimate differences can exist in objectives between an application trying to impress a user, a base station trying to manage overloaded channels, a backhaul aggregator, and the metro network, for instance. So boxes deeper in the network may want to take a peek at suspect packets. "[Still,] I don't think you really need DPI either in the line card or in the metro network," says Thomas Eklund, vice president of marketing and business development at packet-processing chip vendor Xelerated. "Depending on regulations, inspection probably makes the most sense integrated into the access-network fabric. There, you must classify each packet through Layer 4. Beyond that [layer], I would argue it isn't really necessary."

You must also consider the government regulations that Eklund calls Layer 8. The Federal Communications Commission's sudden interest in network neutrality-the idea that the net, including carriers, should treat every packet the same-is of particular concern to equipment and silicon providers. Just what this doctrine means and how it might turn into regulation are areas of anxious debate. "Net neutrality appears to forbid DPI," Eklund observes. "But security, user demands for QOS, and the carriers' need to generate revenue may all require DPI." Such conflicts typically lead to politically driven instability in

regulations and, hence, create a need for great flexibility in switches and routers throughout the network.

#### **ADDRESSING THE SILICON**

From this statement of the problem, you can generalize about the kind of silicon that the next generation of access multiplexers, base stations, and carrier-Ethernet switches and routers will require. First, these chips will have to be fast. Wire speed for a VDSL2 twisted pair may be 100 Mbps. Deeper into the network, all transmission is optical, and a speed requirement of 10s of gigabits per second is not unusual. Switch and router boxes can't run below wire speed and depend on big buffers to make up the difference if carriers are succeeding in getting high channel usage because there would never be enough dead time in which to work through the buffer. And some new media types, notably audio conferencing and videoconferencing, are highly intolerant of the latencies big buffers would create.

The chip or chips must also be able to perform packet inspection. Just how

deep that inspection must go is a matter of great uncertainty. As a generalization, however, the closer to the edge of the network a chip will sit, the more likely it is to have to do DPI. After inspection, the hardware will have to classify the packet and place it in the right queue for export. Further, the system will have to support a growing array of administrative, bookkeeping, supervisory, and errorrecovery protocols.

What does all this mean for the silicon? In simpler times, the hardware was just a fast CPU with a lot of memory sometimes, just an embedded PC. All the functions were in the software. As speeds and functions both grew, however, their product outran Moore's Law. At that point, the hardware architecture split into two planes. Sequential, control-oriented tasks stayed in a CPU in the control plane. The much faster but readily parallelizable packet processing moved to more specialized hardware in the data plane.

Under growing pressure, the data plane evolved further. As data rates grew too high for CPUs to keep up, some architects developed network processors—essentially, microcontrollers with tightly coupled hardware accelerators to handle the bottleneck tasks. Other design teams went in a different direction: a hardware pipeline. Fixed-function hardware engines could keep up with very high wire speeds; if the sequence of

## CADENCE OrCAD RELEASE 16.3 YOUR WINDOW TO THE FUTURE

#### **New Cadence OrCAD Release 16.3**

From front-end design creation with Cadence® OrCAD® Capture and OrCAD Capture CIS to circuit simulation and analysis with Cadence PSpice® A/D and PSpice Advanced Analysis to back-end layout with Cadence OrCAD PCB Editor, the OrCAD family of products has been enhanced in the 16.3 release. By boosting performance and productivity through new features and functionality, this latest release helps deliver shorter, more predictable design cycles for PCB designs.

#### Join EMA for a Free 16.3 Lunch 'n Learn

To learn more about the OrCAD Release 16.3 attend a free "Lunch 'n Learn" in your area. You can register by visiting www.ema-eda.com/orcad16.3 or call us at 800.813.7288.

cādence°

© 2009 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, OrCAD, and PSpice are registered trademarks of Cadence Design Systems, Inc. All others are properties of their respective holders. tasks in packet processing remained the same, simple data flows between pipeline stages eliminated many of the loads and stores inherent in a CPU-centric architecture, saving time and power.

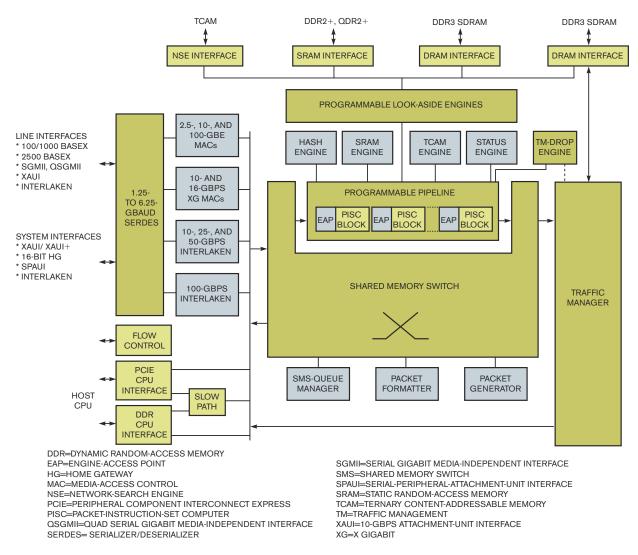

But as protocols grew more diverse and complex, the fixed functions and fixed topologies broke down. Pipeline stages began to look like programmable accelerators. "Life is too risky now for fixed-function pipelines," says Xelerated's Eklund. "Programmability is not necessary only in the access fabric. It has to go much deeper into the network." Pipelines also sprouted thickets of conditional bypass and feedback paths and, eventually, accelerators of their own until the pipeline became just the central engine in a network of processing elements (Figure 1).

#### THE EVOLVING ENGINE

This growing complexity is erasing the distinction between the control and the data planes. At the same time, process migration is yielding less increase in circuit speed. As a result, some architects are returning to where they began: software on a CPU. This time, though, the CPU is a multicore cluster with both general-purpose processors and specific accelerators. Toby Foster, senior product marketing manager at Freescale, describes such a device (Figure 2). "The QorIQ chip family employs multiple e500 Power Architecture cores to cover applications from line cards to base stations and infrastructure," he says. "As the control and data planes merge, we see multicore chips with datapath accelerators-a queue manager, a crypto engine, a regular-expression matcher-encroaching on the traditional ASIC approach."

With all these cores, the traditional bus-based interconnect structure is failing, as well. To get the bandwidth the chip needs, architects provide each processing site, including the accelerators, with local caches, and they may tie everything together through a nonblocking switch fabric. If architects then provide hardware coherency across the caches and fabric, the programming model for the chip can approximate coding for a single CPU.

Even with good cache design, however, scheduling data movement under software control in such a chip involves a lot of work. "Traffic management in a multicore chip creates access issues,"

warns Satish Sathi, senior principal engineer at Applied Micro. "And these issues involve fairness, QOS, and conflicts for resources. You can resolve them in software, but that [approach] creates overhead."

Applied Micro's approach is hardware-based virtualization. In effect, Sathi explains, the control software sets up a route through the engines on the chip for each category of packets. A network of gueues and a hardware-arbitration engine then steer the packets through the maze of engines, buses, and bridges (Figure 3). "The arbitration engine does dynamic arbitration based on actual end-to-end congestion on the chip," Sathi says. "Each packet gets inspected at the end of each task and routed to its next stop."

It's not a coincidence that this scenario sounds remarkably like a networkwith nodes, routers, heterogeneous interconnect, and virtual channels. Increasingly, networking chip architectures are leaving behind the idea of a CPU core with accelerators on a bus and the concept of a CPU controlling a data-plane pipeline. Instead, the chips are becoming miniature models of the networks they will serve: heterogeneous collections of processing and routing sites, heterogeneous interconnect, virtual connections, and hardware-supported explicit routing of packet streams. The ideal we are approaching is the ability to define a virtual data-flow machine for each packet flow on an underlying fabric of programmable engines. Therein may lie the future not only of networking ICs but also of the SOC (system on chip) itself.EDN

#### FOR MORE INFORMATION

Applied Micro www.appliedmicro.com Arcturus Networks www.arcturusnetworks. com Broadcom www.broadcom.com

Continuous Computing www.ccpu.com

You can reach **Executive Editor** at 1-510-744-1263 and ronald.wilson@ reedbusiness.com

www.freescale.com Solarflare Communications www.solarflare.com Verizon www.verizon.com

Xelerated www.xelerated.com

# Freescale Semiconductor

©2008 National Instruments. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. \*Prices subject to change. 2008-9625-301-101-D

### World-Trusted **Data Acquisition**

#### Simple, Secure, Wi-Fi DAQ

- Up to 50 kS/s/ch, 24-bit measurement resolution

- 128-bit AES data encryption

- Starting at \$699<sup>\*</sup>

#### **Multifunction USB DAQ**

- Up to 1.25 MS/s, 16 bits

- Starting at \$159\*

#### **High-Performance PC DAQ**

- Up to 4 MS/s/ch, 16 bits

- PCI and PXI Express options available

- Starting at \$429\*

- >> Find the right DAQ device for your project at ni.com/dag

800 454 6119

TO SERIOUSLY COMPETE WITH HARD-DRIVE MAKERS, SEMICONDUCTOR VENDORS MUST AMASS A ROBUST, SUSTAINED SUPPLY OF SILICON FOR SOLID-STATE DRIVES. THEY ALSO MUST ADDRESS PLENTY OF MISCONCEP-TIONS ABOUT THE NEWER TECHNOLOGY'S CAPABILITIES AND LIMITATIONS.

> lash-memory-based solid-state drives have recently stirred up the staid storage industry, and their initial success stories foretell a potentially stellar future. Consider, for example, how rapidly they've taken over the formerly robust market for 1.8-in. hard-disk drives. Also consider their significant influence on smaller-form-factor hard-disk drives' lackluster initial unveilings. A notable percentage of netbook, tablet, and other alternative mobile computers, especially

those running Linux operating-system variants, contain solid-state drives instead of hard-disk drives. Thin and light conventional notebook PCs running Windows and OS X are also well along the conversion path.

Enterprise-computing applications might at first glance seem to be poor candidates for solid-state technology, given its substantially higher cost than the magnetic alternative at the high capacities that this market segment requires. Yet, by virtue of its low energy consumption, increased reliability, and ultrafast read rates, the technology is making notable progress in conquering the corporate world. Consider that, to maximize hard drives' performance, IT departments have long formatted only the platters' fastest-access portion, wasting the rest of the drive and thereby blunting the argument that hard drives cost less than their nonmagnetic counterparts. Consider, too, that a number of applications, including smartphones, PDAs (personal digital assistants), digital still cameras, and videocameras, that might have formerly gone with—and, in some cases, in initial product generations, did go with-hard drives have migrated en masse to solid-state storage.

Proponents of both approaches dispute the extent of solid-state technology's potential to obsolete its predecessor, and the industry has yet to determine a winner. These debates illustrate a number of fundamental misrepresentations of solid-state drives' strengths and shortcomings. *EDN* readers' feedback to past editorial coverage reveals similar misunderstanding (**Reference 1**). This article attempts to clear up at least some of that confusion.

Cost, power consumption, and any other all-important comparative factors aside, the differences between hard-disk and solid-state drives boil down to a few fundamental points. First, solid-state drives, especially those in applications with random-access patterns, read data substantially faster than hard drives can, assuming the absence of any storageto-system-interface bottlenecks. In contrast, solid-state drives, especially those in applications with random-access patterns, write data much slower than hard drives do. Also, once the solid-state drive has depleted its inventory of spare capacity, block-erase delays become a larger percentage of the total write latency. Further, unlike with a hard-disk drive, flash memory is not fully bit-alterable. Although flash memory can change ones to zeros on a bit-by-bit basis, converting even a single zero back into a one requires erasing the entire block containing the bit.

Another difference is that flash memory eventually "wears out" after extended erase cycles. However, it tends to do so on a blockby-block basis and in a predictable manner that the media controller can easily detect far in advance and compensate for in a variety of ways. Many hard-drive failures, in contrast, are abrupt and systemic. Further, because solid-state drives are semiconductorbased, they are notably more immune to the effects of abrupt shock, sustained vibration, and other types of jarring. They're also comparatively impervious to environmental interference, such as from magnetic fields.

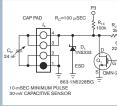

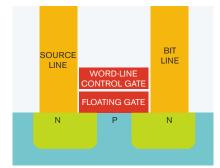

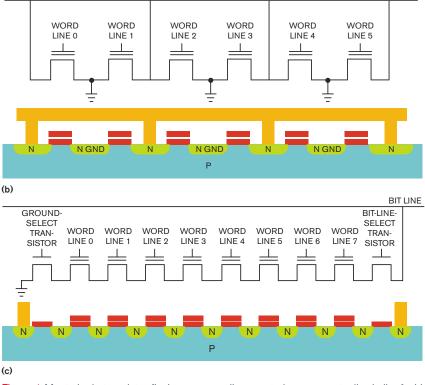

Most of today's flash memory uses a conceptually common floating-gate cell structure (Figure 1). Fast-random-readaccess NOR and slower—albeit less expensive on a per-bit basis—NAND technologies differ predominantly in their cell-to-cell interconnect schemes. In its default erased state, the transistor turns on—that is, outputs a one—when the memory device's integrated address-decoding circuitry activates the necessary

(a)

array row and column lines to select it. With the transistor programmed by means of additional electrons stored on its floating gate, it cannot turn on when address inputs select it and therefore outputs a zero to read attempts.

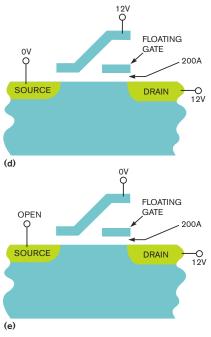

Altering the stored value of a flashmemory transistor involves the application of higher-than-normal voltages to various transistor junctions, thereby creating the necessary electric fields to affect electron flow onto or off the floating gate. Initial flash-memory generations required off-chip generation of these voltages; nowadays, most devices employ on-die high-voltage pumps for this function. Theoretically, you could alter a transistor's value-both for oneto-zero programming and for zero-toone erasure-on a bit-by-bit basis, as is the case with EEPROMs (electrically erasable programmable read-only memories), FRAMs (ferroelectric randomaccess memories), MRAMs (magnetic RAMs), and battery-backed SRAMs (static RAMs). The necessary signalrouting, isolation, and other circuitry, BIT LINE

FROM AN EFFICIENCY STANDPOINT, SOLID-STATE DRIVES AND THE NAND CHIPS WITHIN THEM PREFER TO WRITE DATA IN APPROXIMATELY 4-KBYTE CHUNKS.

however, would use too much die area and would therefore be too expensive at the IC capacities that bulk-storage applications require.

With modern NAND flash memory, on the other hand, you can erase blocks in approximately 512-kbyte increments. Bit-by-bit programming is possible; from an efficiency standpoint, however, solidstate drives and the NAND chips within them prefer to write data in approximately 4-kbyte chunks. This preference reflects the cost-versus-performance sizes of the RAM buffers on the flash-memory die. The bulk-alteration requirement differentiates flash memory not only from other nonvolatile semiconductor-

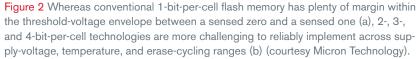

Figure 1 Most single-transistor flash-memory cells operate in a conceptually similar fashion (a) regardless of whether they interconnect in a NOR (b) or a NAND (c) scheme. Bit-by-bit or more efficient page-by-page programming places incremental charge on the floating gate (d), thereby counteracting an applied turn-on voltage during subsequent reads. Block-by-block erasure (e) removes this charge surplus (courtesy the Wikipedia Foundation). storage technologies but also from harddisk drives. The repeated electron flow across the thin silicon layer between the flash-memory transistor's substrate and floating gate and through incremental program and erase cycles stresses the oxide. At first, electrons inadvertently become trapped in the oxide lattice, impeding the flow of other electrons and slowing subsequent program and erase operations. Eventually, the oxide breaks down by rupturing, for example, leading to fundamental transistor failure. This demise tends to disrupt the function of the entire erase block that contains the affected transistor.

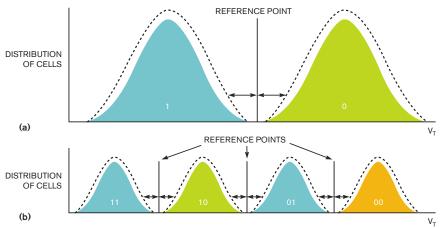

Modern flash memories come in both SLC (single-level-cell) and MLC (multilevel-cell) variants; today's MLC variants are primarily 2-bit-per-cell devices (Figure 2). With SLC flash memories, the voltage-sensing circuitry that connects to the array transistors' outputs can be relatively simple because it needs to discern only one voltage threshold and because the transistor's one and zero output voltages have substantial margin to this threshold. However, with a 2-bit-per-cell MLC flash memory, three voltage thresholds-that is, four levels-require discernment during reads. The programming operation for placing the necessary amount of electron charge onto the transistor's floating gate is similarly precise, and the effects of supply-voltage and operatingtemperature variation and cycling further complicate this operation. Span-

#### AT A GLANCE

Solid-state storage offers many benefits over the currently dominant rotating magnetic alternative, but key differences require consideration and accommodation.

Operating systems and their underlying file systems make assumptions about mass storage's long-latency random accesses and full bit alterability. Neither assumption is valid in the flash-memory era.

Both operating systems' and system firmware's full support for a new ATA (advanced-technologyattachment) command promises to substantially simplify the flash-media controller's task, thereby boosting write performance.

Deprating systems can make key customizations to their functions once they know that they're talking to a solid-state drive instead of a hard-disk drive.

Hardware evolutions, by discarding vestigial interfaces and extraneous functions, can notably optimize systems' solid-state drive implementations.

sion claims that its MirrorBit MLC technology approach somewhat reduces the need for precise electron placement. Nonetheless, the concept remains largely relevant.

It's probably no surprise that MLC reads and writes—that is, programs are substantially slower than their SLC

counterparts and that the maximum block-cycling specifications for MLC memories are on average an order of magnitude less than those of SLC chips. These fundamental trade-offs are necessary for obtaining a lower per-bit cost for MLC storage devices (**Table 1**).

Now, consider Intel and Micron Technology's new 3-bit-per-cell memories and that Sandisk recently began producing 4-bit-per-cell X4 devices (Reference 2). The difference between any two sequential voltage levels and, hence, decoded-bit combinations with these new devices is on the order of 100 or so electrons or fewer in some cases. This situation represents a profound challenge for semiconductor-process and -product engineers. By potentially hampering both performance and data dependability, it calls into question the chips' suitability for applications requiring highly reliable storage. Then again, folks not too long ago were saying the same thing about 2bit-per-cell MLC flash memory.

#### **CONTROLLER CHOICES**

The media controller may be a hardware-centric device, a software-fueled CPU, or any combination thereof. The hardware-versus-software choice of a controller involves trading off cost, performance, and power consumption versus flexibility and the ability to upgrade. Whatever its composition, the media controller acts as a bridge between the flash memories and the conventional hardware and software interfaces that the CPU, core-logic chip set, and other subsystems expect. The controller also manages the data stored in the singlecomponent or multicomponent merged flash-memory array to avoid "hot-spot" overcycling of any erase blocks in the array, ideally as a background function that is invisible to the host both in access time and in any other regard. The controller leverages flash memory's strengths and mitigates its read- and write-speed weaknesses. The result is, with any luck, at least on par withand, ideally, much faster than-the hard-drive alternative.

One perhaps obvious way of boosting effective solid-state-drive performance at the expense of incurring higher power consumption is to access multiple components in parallel using several address-, data-, and control-line channels

| TABLE 1 REPRESENTATIVE 1- AND 2-BIT-PER-CELL NAND-FLASH-MEMORY SPECIFICATIONS |                                 |                                  |                                 |                                  |                                      |                                   |  |

|-------------------------------------------------------------------------------|---------------------------------|----------------------------------|---------------------------------|----------------------------------|--------------------------------------|-----------------------------------|--|

| Technology                                                                    | Erase specification<br>(cycles) | Program-page<br>size<br>(kbytes) | Erase-block<br>size<br>(kbytes) | Random-read<br>latency<br>(μsec) | Per-page<br>program time<br>(kbytes) | Per-block<br>erase time<br>(msec) |  |

| SLC (1-bit-per-<br>cell) flash memory                                         | 100,000                         | 4                                | 512                             | 25                               | 250                                  | 2                                 |  |

| MLC (2-bit-per-<br>cell) flash memory                                         | 10,000                          | 4                                | 512                             | 50                               | 900                                  | 2                                 |  |